Grandes modelos de linguagem, geradores de imagens, assistentes inteligentes - a IA está a consumir enormes quantidades de energia.

Um grupo de investigação chinês descreve agora um caminho surpreendentemente simples para reduzir drasticamente esse consumo, sem sacrificar a precisão.

A actual vaga de IA tem um lado menos visível: centros de dados a trabalhar no limite, sistemas de refrigeração sobrecarregados e contas de electricidade a disparar. Em especial, o treino de modelos de grande dimensão faz subir consumo e custos para valores difíceis de sustentar. Investigadores na China apresentam uma abordagem que pode baixar radicalmente a energia necessária para treinar redes neuronais - mantendo, ao mesmo tempo, um desempenho competitivo.

Porque é que a IA moderna consome tanta electricidade

Seja um chatbot, um gerador de imagens ou um sistema de assistência à condução, por trás do serviço existem grandes clusters de computação com chips especializados. O treino de redes neuronais profundas exige milhões a milhares de milhões de operações matriciais, e a indústria tem dependido sobretudo de GPUs (processadores gráficos) para executar esse trabalho.

Nesta arquitectura, há duas fontes principais de consumo energético:

- o cálculo propriamente dito nos processadores e nas GPUs

- a movimentação incessante de dados entre a memória e as unidades de computação

É precisamente neste segundo ponto - o “vai e vem” de dados - que entra o novo caminho: calcular directamente na memória, com uma base de hardware diferente.

Memristores: componentes que “se lembram” (e porque isso importa para a IA)

O conceito-chave é o memristor. De forma simplificada, trata-se de um resistor com memória: a sua resistência eléctrica depende do estado em que foi “programado” anteriormente, e esse estado mantém-se.

Isto torna os memristores especialmente interessantes para representar fisicamente os pesos de uma rede neuronal. Em vez de guardar números numa memória convencional e os enviar continuamente para um processador, as operações podem acontecer no mesmo local onde os pesos estão armazenados. Em teoria, esta computação in-memory permite poupanças energéticas muito grandes.

Na prática, porém, existe um obstáculo relevante: memristores não são perfeitos. Apresentam ruído, variabilidade e respostas que não são totalmente exactas. Pequenos desvios podem desestabilizar o treino e degradar resultados se o método não for pensado para lidar com essa realidade.

O desafio central não é eliminar por completo a imprecisão do hardware, mas aprender a operar com ela - em vez de a compensar com correcções energeticamente dispendiosas.

Método de treino EaPU: não combater o erro, mas incorporá-lo

É aqui que surge a técnica apresentada pela equipa do laboratório de Zhejiang: “actualização probabilística ciente do erro” (error-aware probabilistic update), abreviada como EaPU. A ideia, bastante intuitiva, é aceitar pequenas diferenças - desde que se mantenham dentro de um limite de tolerância.

Como funciona a EaPU, na essência (memristores + IA)

No treino clássico, após cada iteração, a rede ajusta uma grande parte dos seus pesos. Em hardware de memristores, isso é problemático porque reescrever o estado dos dispositivos pode exigir muita energia e acelerar o desgaste.

A EaPU altera o processo desta forma:

- o sistema tolera pequenas discrepâncias quando ficam abaixo de um limiar definido

- só reescreve um peso no memristor quando a alteração é realmente relevante

- em cada ronda de aprendizagem, o modelo actualiza menos de 0,1% de todos os parâmetros

Com isto, o maior custo energético do treino em memristores - reprogramar continuamente um grande número de células - é reduzido de forma substancial.

Consumo muito mais baixo e vida útil muito maior do hardware

Segundo os autores, ao comparar com métodos anteriores baseados em memristores, observam-se vários ganhos simultâneos:

- até 50× menos energia no treino em hardware de memristores

- até 1.000× mais vida útil dos dispositivos, por serem reescritos com muito menos frequência

- cerca de 60% mais precisão face a abordagens de treino mais antigas para memristores

O contraste com uma solução tradicional baseada em GPUs é ainda mais marcante. A equipa indica que, para a mesma tarefa, a EaPU pode reduzir o consumo energético em cerca de seis ordens de grandeza - ou seja, aproximadamente um milhão de vezes menos energia do que uma configuração comparável com GPUs.

Uma redução do consumo energético face a sistemas GPU na ordem de 10^6 teria impacto directo no custo, na escala e na sustentabilidade da IA actual.

Testes iniciais: remover ruído e melhorar resolução de imagens

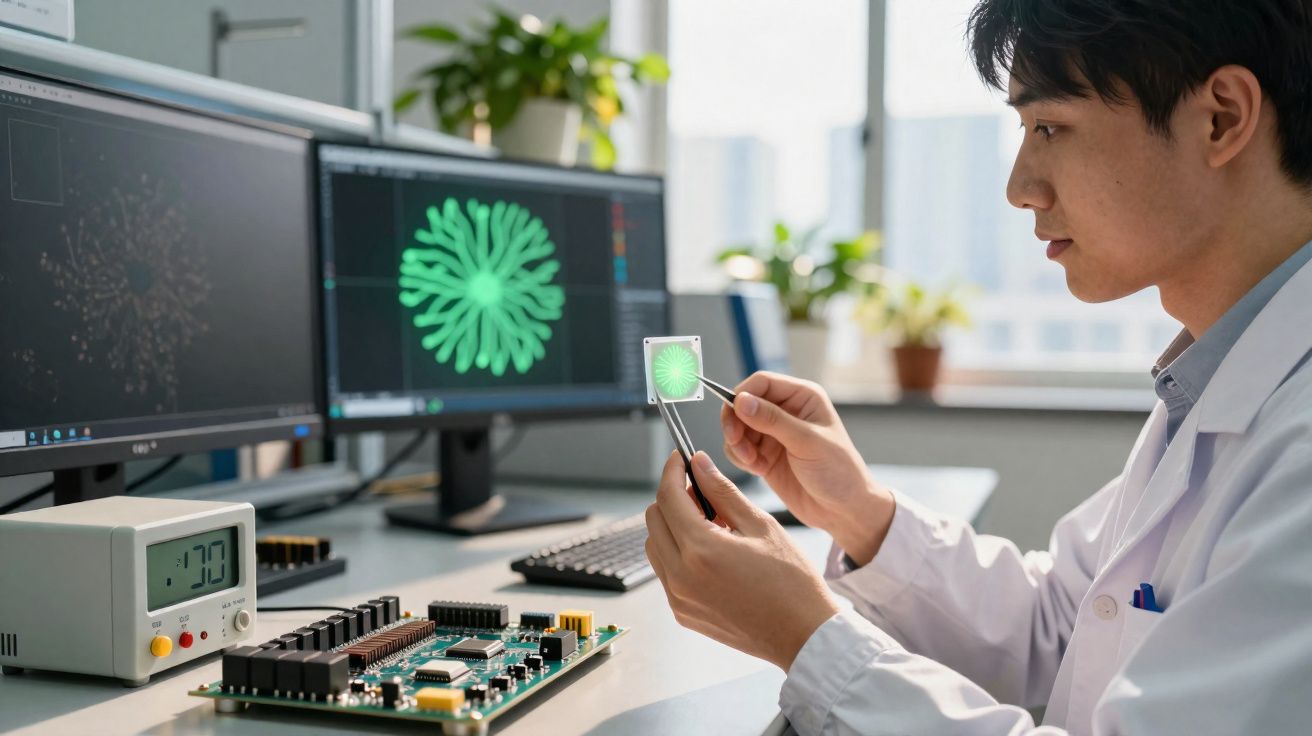

A técnica EaPU já foi validada em testes práticos, usando uma matriz de memristores com 180 nm de largura de estrutura. Foram treinadas redes neuronais em duas tarefas comuns de visão por computador:

- remoção de ruído em imagens

- aumento artificial de resolução (super-resolution)

Os resultados ficaram em linha com métodos consolidados em hardware convencional - mas com muito menos energia. Isto sugere que a proposta não é apenas teórica: faz sentido em cenários reais de processamento de imagem.

E os grandes modelos de linguagem: podem beneficiar?

Por agora, a dimensão do hardware disponível limita a escala dos testes. Os chips de memristores usados ainda são relativamente pequenos. Ainda assim, a equipa defende que a lógica da EaPU é compatível, em princípio, com grandes modelos de linguagem (LLM, Large Language Models).

Se essa hipótese se confirmar, o efeito poderá estender-se a sistemas que hoje dependem de recursos gigantescos - como chatbots, assistentes de programação e ferramentas de análise. O plano passa por validar a técnica em redes consideravelmente maiores.

Há também outro ponto relevante: a abordagem não teria de ficar restrita a memristores. Os investigadores sugerem que pode ser adaptada a outras memórias emergentes, como:

- transístores ferroeléctricos

- RAM magnetorresistiva (MRAM)

Isto alarga o leque de opções para construir hardware de IA energeticamente eficiente.

O que isto pode mudar em centros de dados e no “edge”

Se a abordagem escalar, os centros de dados orientados para IA poderão evoluir para arquitecturas bastante diferentes. Em vez de filas de servidores cheios de GPUs, pode tornar-se viável usar chips analógicos compactos que unem armazenamento e computação. O impacto não se limita à factura energética: também reduz a necessidade de refrigeração e o rasto de carbono associado.

Consequências plausíveis incluem:

- ciclos de treino significativamente mais baratos para empresas

- chips de IA mais pequenos e especializados para telemóveis, automóveis e indústria

- mais processamento no edge (à beira da rede), evitando enviar dados constantemente para a cloud

No quotidiano, isto pode desbloquear funcionalidades inteligentes onde hoje o consumo é impeditivo - por exemplo, sensores alimentados a bateria, wearables e robôs autónomos.

Novo contexto (adicional): para além da poupança directa, técnicas como a EaPU podem facilitar metas de eficiência energética impostas por políticas internas de sustentabilidade e por exigências de reporte ambiental. À medida que a IA entra em mais serviços públicos e empresariais, a pressão para reduzir consumo e calor gerado em infra-estruturas torna-se um factor de competitividade, não apenas de “responsabilidade”.

Conceitos essenciais: computação in-memory analógica e tolerância ao ruído

Para quem não acompanha de perto o tema de hardware, dois termos são centrais aqui:

- Computação in-memory analógica: as operações são feitas dentro do próprio bloco de memória, recorrendo a correntes e tensões analógicas, em vez de apenas lógica digital (zeros e uns).

- Tolerância ao ruído: o modelo é treinado para continuar estável e fiável mesmo quando os sinais e as actualizações têm imprecisões ou ruído.

É relevante notar que as redes neuronais já possuem alguma robustez natural a perturbações. A EaPU aproveita esse “espaço de manobra” de forma deliberada, em vez de procurar uma exactidão matemática máxima que, muitas vezes, não é necessária para bons resultados práticos.

Riscos, perguntas em aberto e o que pode acontecer a seguir

A proposta não elimina todas as dúvidas. Continua por esclarecer, por exemplo, como a EaPU se comporta em modelos extremamente grandes, com milhares de milhões de parâmetros. Também permanece incerto o custo real de fabricar chips de memristores suficientemente fiáveis e consistentes à escala industrial.

Em aplicações críticas - como medicina ou condução autónoma - há ainda uma camada adicional de risco: é indispensável definir limites rigorosos para a imprecisão do hardware e demonstrar, com validação extensa, que a tolerância ao ruído não compromete margens de segurança.

Novo contexto (adicional): outro desafio provável será a adopção no ecossistema: ferramentas de desenvolvimento, bibliotecas de treino e métodos de validação terão de amadurecer para suportar, de forma padronizada, hardware analógico in-memory. Sem esse suporte, a tecnologia pode ficar confinada a protótipos, mesmo que os ganhos energéticos sejam fortes.

Ainda assim, a mensagem é clara: o caminho para modelos de IA cada vez maiores não precisa de terminar numa “armadilha” energética. Quando hardware e algoritmos de treino são concebidos em conjunto, é possível reduzir de forma significativa a electricidade necessária - e aproximar o cenário em que um modelo potente corre num único chip eficiente.

Comentários

Ainda não há comentários. Seja o primeiro!

Deixar um comentário